Registre, contoare, cronometru

Lucrări de laborator Nr. 2 Registre și contoare. Cronometru.

Funcțiile dispozitivelor digitale, desigur, nu se limitează la implementarea diferitelor FAL. Am dori să folosim dispozitive digitale pentru prelucrarea informațiilor, calcule. Dar pentru a implementa aceste posibilități, ne lipsește un element de memorie care ar putea stoca rezultate intermediare. La urma urmei, este imposibil să faci un calculator dacă nu există nicio modalitate de a salva numerele introduse și rezultatul calculului.

Elementul de memorie este unul dintre cele mai importante elemente ale dispozitivelor digitale. Pentru a nu face greșeli la proiectarea dispozitivelor digitale, este necesar să înțelegeți locul acestui nod, ideea acestuia și instrumentele de limbaj Verilog asociate acestuia.

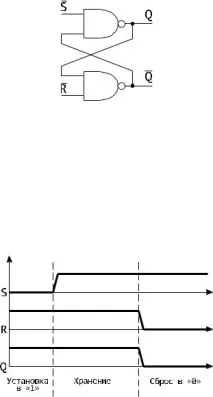

Primul element de memorie pe care îl vom lua în considerare este un zăvor (latch în engleză) zăvorul este baza tuturor elementelor de memorie. Este format din două

elemente (sau din două elemente, în funcție de baza aleasă în timpul proiectării), conectate după următoarea schemă:

Încuietoarea are două intrări și două ieșiri. Intrările sunt semnale „resetare” și „setat la unu” sau „resetare” și „setare”. În funcție de elementele care alcătuiesc zăvorul, polaritatea semnalelor de intrare se va modifica. În principiu, o resetare și o setare apar atunci când semnalele R sau S sunt la zero, deci sunt notate ca și pentru a reflecta acest fapt. Ieșirea unui latch este bitul de date pe care îl stochează. Cele două ieșiri diferă în polaritate - una dintre ele inversează bitul stocat. Mai jos este un tabel cu toate combinațiile posibile de semnale de intrare și o diagramă de timp a zăvorului.

Să descriem zăvorul în limbajul Verilog, pe baza structurii sale, pe care am considerat-o mai sus. Avem nevoie de două intrări, două ieșiri și douăelement pe care îl vom descrie cu ajutorul AND (operator &) și NOT (operator

modul latch_structure( intrarea nR,

intrare nS, ieșire Q, ieșire nQ);

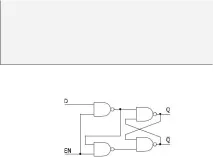

În primul rând, avem nevoie de un element de memorie pentru stocarea datelor. Pentru a face zăvorul mai convenabil de utilizat, vom schimba ușor schema de conectare a semnalului de control.

Latch-ul va funcționa acum după cum urmează: când intrarea „activare” este ridicată, datele de la intrarea „date” vor trece prin zăvor către ieșire, când intrarea „activare” este scăzută, zăvorul se va salva la ieșire ultima valoare de la intrarea „date”, care a fost înainte ca semnalul „activare funcționare” să fie comutat.

După cum am spus deja, nu este întotdeauna convenabil să folosiți descrieri structurale. În cele mai multe cazuri, folosirea unei descrieri comportamentale este mult mai eficientă. Descrierea comportamentală este adesea formulată mult mai concis și, pentru că este mai ușor de înțeles pentru un om, lizibilitatea codului este îmbunătățită și șansa de a scrie erori este redusă.

Să descriem zăvorul în Verilog folosind abordarea comportamentală:

modul d-latch_behave( intrarea d,

input en, output reg q);

întotdeauna @(en, d) începe dacă (en) q se termină

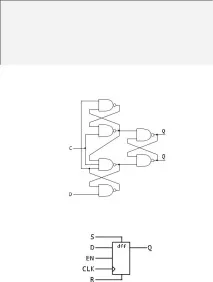

Dacă mai adăugăm două zăvoare la acest circuit, atunci putem lega modificarea „conținutului” zăvoarei la tranziția semnalului de control de la „0” la „1”, atunci obținem următoarea structură:

Această schemă poate fi ușor modificată prin introducerea semnalelor de control pentru resetare, setare la unu și activare a funcționării. Simplificată, o astfel de schemă este descrisă după cum urmează.

Acest circuit a primit cea mai largă aplicație în circuitele digitale și se numește (de la cuvântul „date” - date). Mai jos este diagrama de timp a funcționării

Rețineți că semnalul Cse numește semnal „ceas” sau „semnal de sincronizare”. De obicei, acest semnal este un semnal de la o sursă externă (cel mai adesea un rezonator de cuarț) cu o frecvență stabilă. Și dispozitivele digitale în sine, pentru care este necesar un semnal de sincronizare, sunt numite sincrone.

Semnalul ceasului joacă un rol foarte important în dispozitivele digitale. În primul rând, este necesar pentru a evita comportamentul imprevizibil și instabil al flip-flops în dispozitivele digitale.

Să descriem un astfel de declanșator pe Verilog:

modul d-flipflop_beahv( intrarea d,

input clk, input rst, input en, output reg q);

întotdeauna @( posedge clk sau posedge primul) beginif (primul) q

else if (en) q end

Descrierea are un nou cuvânt cheie posedge. Este folosit doar în lista de sensibilitate a blocului mereu și înseamnă evenimentul de tranziție a semnalului, al cărui nume este după acest cuvânt cheie, de la starea „0” la starea „1”.

Cuvântul cheie posedge a fost introdus în primul rând pentru a descrie scheme care conțin flip-flops. La urma urmei, declanșatorii, așa cum am spus deja, își pot schimba starea numai în momentul unei margini pozitive (margine pozitivă în engleză) a semnalului de sincronizare.

Adăugarea primului eveniment posedge la lista de sensibilitate vă permite să descrieți comportamentul declanșatorului în momentul resetarii asincrone: de îndată ce apare prima tranziție

de la „0” la „1” blocul întotdeauna este declanșat și verificarea condiției dacă (prima) dă un rezultat pozitiv, declanșatorul este resetat la „0”.

Dacă combinați mai multe flip-flops într-un grup, obțineți ceea ce se numește un „registru” în circuitele digitale. Iată o descriere a registrului în limba Verilog:

modul register_beahv( input [7:0]d,

input clk, input first, input en,

ieșire.reg[7:0] q);

întotdeauna @( posedge clk sau posedge primul) beginif (primul) q

else if (en) q end

Elementele de memorie ne permit să stocăm informații pentru prelucrare ulterioară sau să stocăm rezultatul final al unui calcul, să stocăm rezultate intermediare.

Amintiți-vă descrierea registrului. Este folosit în proiectarea aproape oricărui dispozitiv digital care utilizează Verilog.

Este necesar să remarcăm un concept important al limbajului Verilog. Variabile

Tipurile reg pot fi modificate numai în cadrul aceluiași bloc întotdeauna. Variabilele sunt disponibile pentru verificare în oricare dintre blocuri, dar valoarea lor poate fi modificată doar într-unul dintre ele.

întotdeauna @( posedge clk) începe dacă (în

întotdeauna @( posedge clk) începe dacă (n > 5) începe

b else b module counter_8bit( input clk,

introduceți ro, introduceți mai întâi,

outputreg[7:0]contor);

întotdeauna @( posedge clk sau posedge primul) beginif (primul) contor

else if (en) counter end

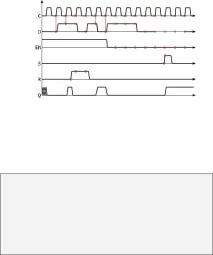

Pentru a putea număra evenimente, și nu tranziții ale semnalului de sincronizare de la „0” la „1”, va trebui să introduceți un alt circuit. Semnificația și scopul acestuia sunt următoarele: trebuie să obținem un semnal sincron de durată unitară de la un eveniment asincron. Apoi, aplicând un astfel de semnal la intrarea de activare a contorului, putem număra numărul de evenimente care au avut loc.

Mai jos este o diagramă pentru a face acest lucru:

Un exemplu despre cum funcționează o astfel de schemă:

Desigur, o astfel de schemă funcționează numai atunci când semnalul de intrare se schimbă la o frecvență mai mică decât frecvența ceasului.

Semnalul de ieșire în acest caz este conectat la intrarea de activare a contorului.

Dispozitivele digitale sunt structuri modulare. Ele constau din blocuri de bază interconectate. Structura dispozitivelor digitale poate să semene cu meșteșugurile dinLEGO, unde structura întregului este determinată de utilizarea și conectarea corectă a pieselor mici.

Avem deja suficiente blocuri pentru a proiecta primul nostru dispozitiv digital - un cronometru.

Cronometrul ar trebui să funcționeze după cum urmează: prin apăsarea butonului START, cronometrul pornește și începe să numere timpul cu o precizie de sutimi de secundă. Valoarea curentă a timpului este afișată continuu pe patru indicatori cu șapte segmente. Apăsarea din nou a butonului START oprește numărătoarea inversă. Când apăsați butonul RESET, cronometrul se oprește și valoarea sa actuală este resetata.

Începeți dezvoltarea unui cronometru prin întocmirea unei diagrame bloc a unui dispozitiv digital - „asamblați” din blocurile de construcție de care știți deja că veți avea nevoie și apoi combinați-le într-un singur dispozitiv.

Începeți cu blocuri mari. Definiți-le funcțiile. Astfel, veți ști ce funcții trebuie implementate și veți selecta compoziția necesară a blocurilor de bază pentru acestea.

De exemplu, pentru a afișa valorile pe indicatorii cu șapte segmente, veți avea nevoie de decodoare similare cu cele pe care le-am folosit în prima lucrare de laborator. Dar de unde își vor lua ei valorile?

Puteți număra timpul folosind contorul. Deoarece cunoaștem frecvența impulsurilor de ceas - 50 MHz, putem spune că o sutime de secundă corespunde trecerii a 500.000 de impulsuri de ceas.

Puteți compara două numere codificate în cod binar în tehnologia digitală folosind un comparator - unul combinațional care are doi vectori de lungime egală la intrare și iese „1” dacă vectorii se potrivesc și „0” dacă nu se potrivesc.

Folosiți supape separate dacă este necesar.

După ce ați întocmit o diagramă bloc sub forma unei imagini, continuați să descrieți acest circuit în limbajul Verilog.Amintiți-vă că constructele de limbaj vă permit să descrieți concis comportamentul circuitelor digitale, dar nu servesc la efectuarea anumitor acțiuni.

De exemplu, constructul if (a[7:0] = b[11:3]) va face ca un comparator să apară în circuit. Conexiunea acestui comparator va fi determinată de cât de exact utilizați dacă